Research Interests

Mixed-Signal Integrated Circuits:

• Communications: Circuits for High speed wireline communication over copper and fiber optic cables

• Memories: Low-power and reliable Memories and Deep-subthreshold Sense Amplifier Circuits

• Machine Learning: Mixed-signal circuits for energy efficient computing for deep learning accelerators

Photonic Integrated Circuits:

• CMOS-Photonic Intagration: Die-to-Die CMOS-Photonic interfaces

Publications

Refereed Journal Papers:

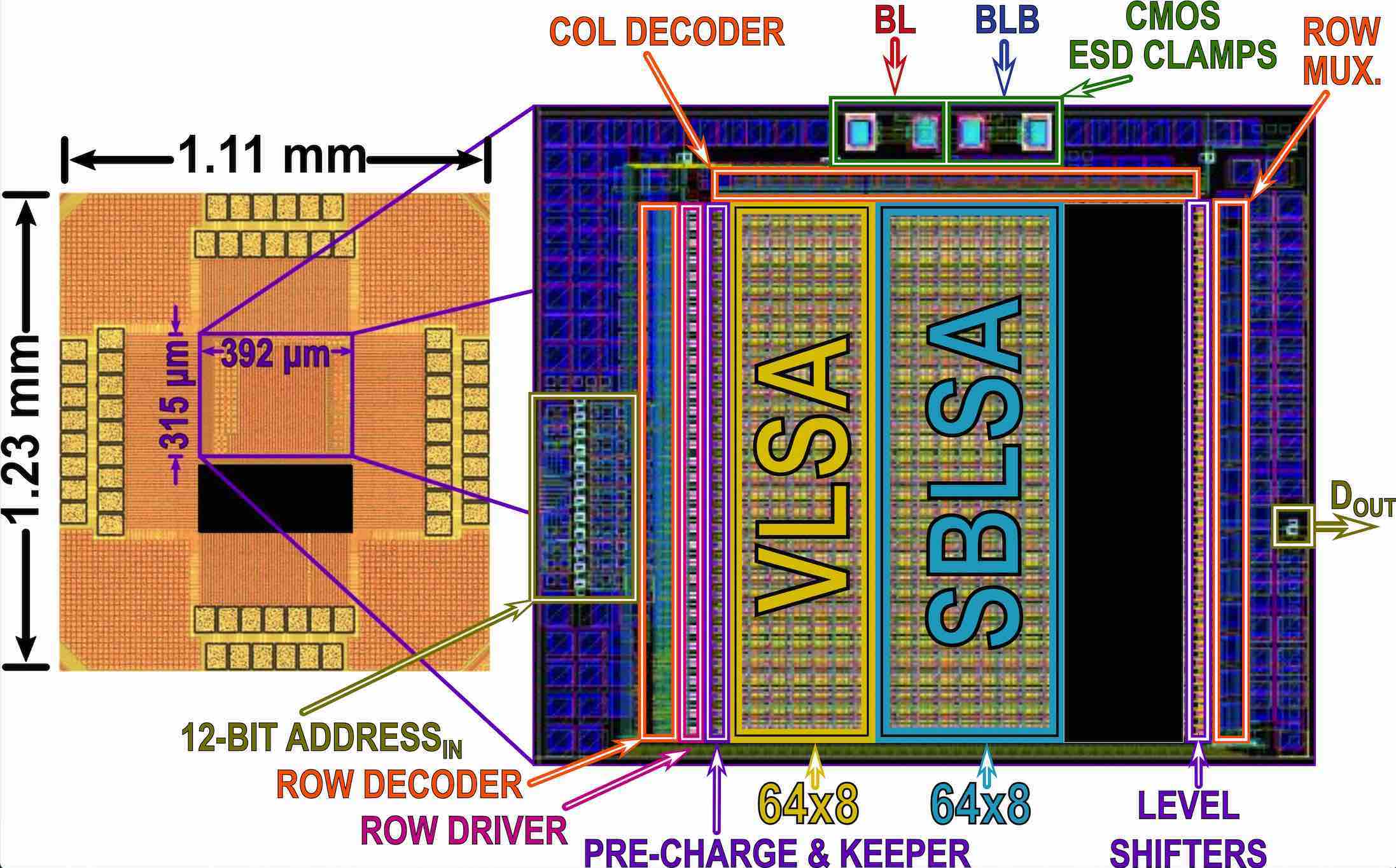

[J2] D. Patel, A. Neale, D. Wright and M. Sachdev, "Hybrid Latch-Type Offset Tolerant Sense Amplifier for Low-Voltage SRAMs," in IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I). Pages: 1-14. [PDF] [IEEExplore Link]

[J1] D. Patel and M. Sachdev, "0.23-V Sample-Boost-Latch-Based Offset Tolerant Sense Amplifier," in IEEE SolidState Circuits Letters (L-SSC), vol. 1, no. 1, pp. 6-9, Jan. 2018. [PDF] [IEEExplore Link]

Refereed Conference Papers, Posters and Presentations:

[C1] D. Patel, D. Wright and M. Sachdev, "Sense amplifier offset characterisation and test implications for low-voltage SRAMs in 65 nm," in 2018 IEEE 23rd European Test Symposium (ETS), Bremen, 2018, pp. 1-6. [PDF] [Slides] [IEEExplore Link]

[C2] D. Patel and M. Sachdev, "Sample-Boost-Latch Based Offset Tolerant Sense Amplifier for Sub-threshold SRAMs" IEEE 2018 International Solid-State Circuits Conference (ISSCC) Student Research Preview, San Francisco, California. [Poster] [Slides] [Research Gate Link]

Submitted Work Under Review:

Research Experience

CMOS Optical Receiver Circuits: University of Toronto

Sept 2016-Present, Advisor: Prof. Anthony Chan Carusone

• Designing Optical Receiver Front-end for +100 Gb/s PAM-4 fiber-optic communications in 16 nm FinFet CMOS

• Providing compact package level integration solution of CMOS optical receiver with state-of-the-art photodetectors

• High-frequency and Low-noise layout optimization in 16 nm FinFet CMOS

• Second order system optimization with Gain-BW-Noise trade-offs and peak-distortion analysis

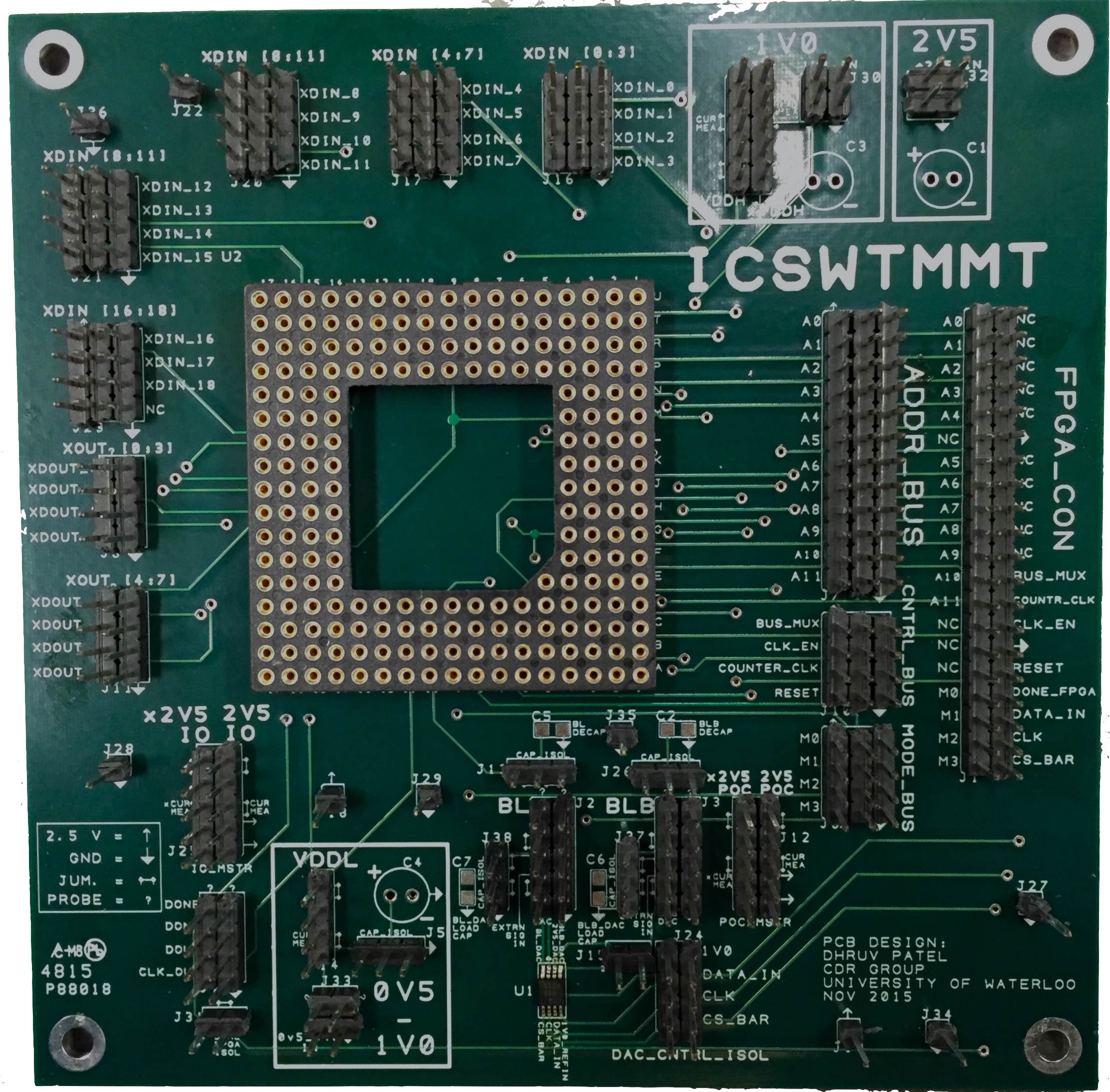

SRAM VLSI Circuits: University of Waterloo

Sept 2015-Aug 2017, Advisors: Prof. Manoj Sachdev, Prof. Adam Neale and Prof. Derek Wright

• Taped-out low-voltage and offset reducing Sense-amplifiers in 65 nm CMOS

• Researched variation tolerant, low-voltage, short-sensing delay sense amplifiers for SRAMs

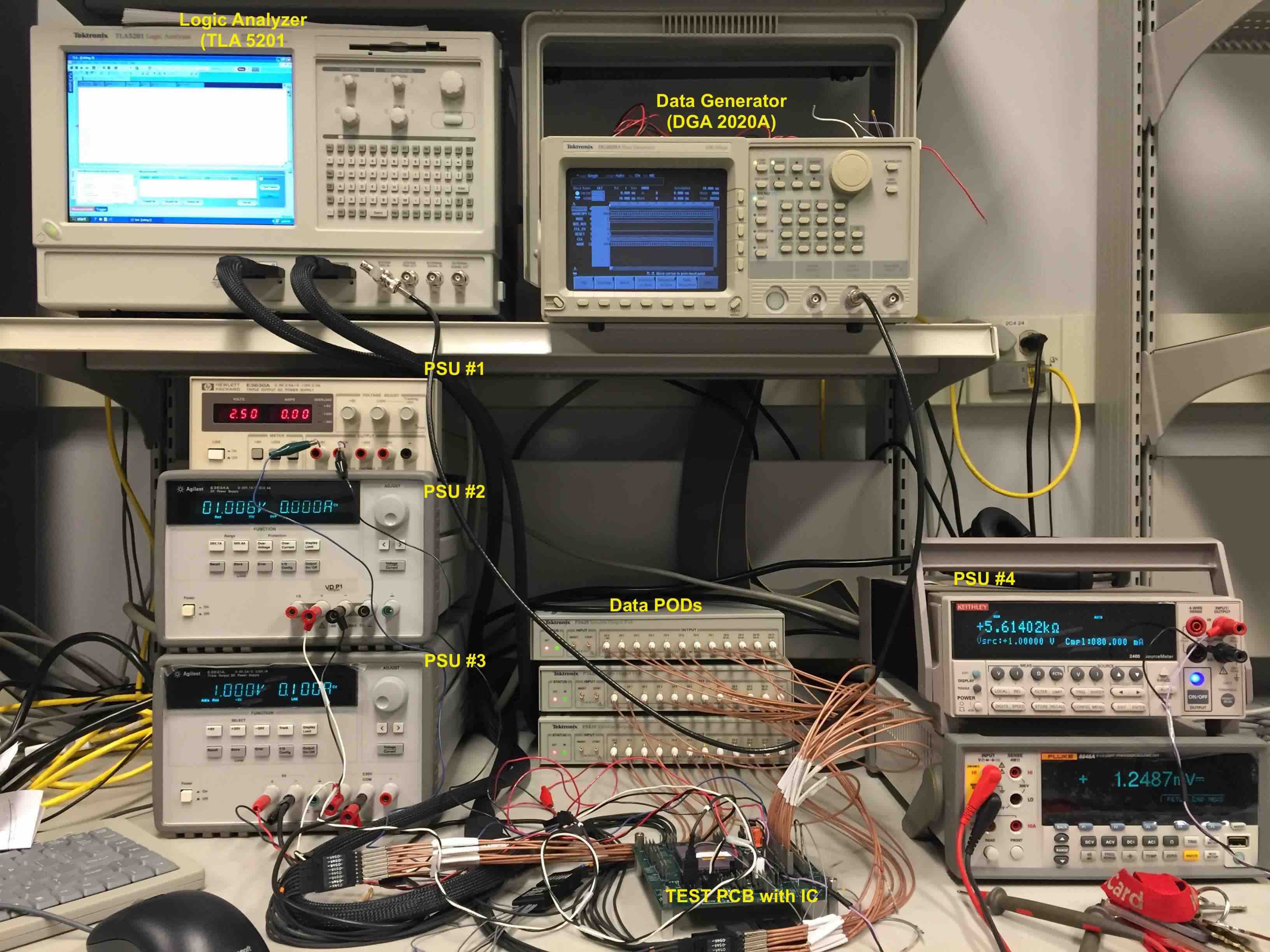

• PCB Design for Sense Amplifier IC characterization

• Characterization of 65-nm Sense Amplifier ICs in VLSI laboratory

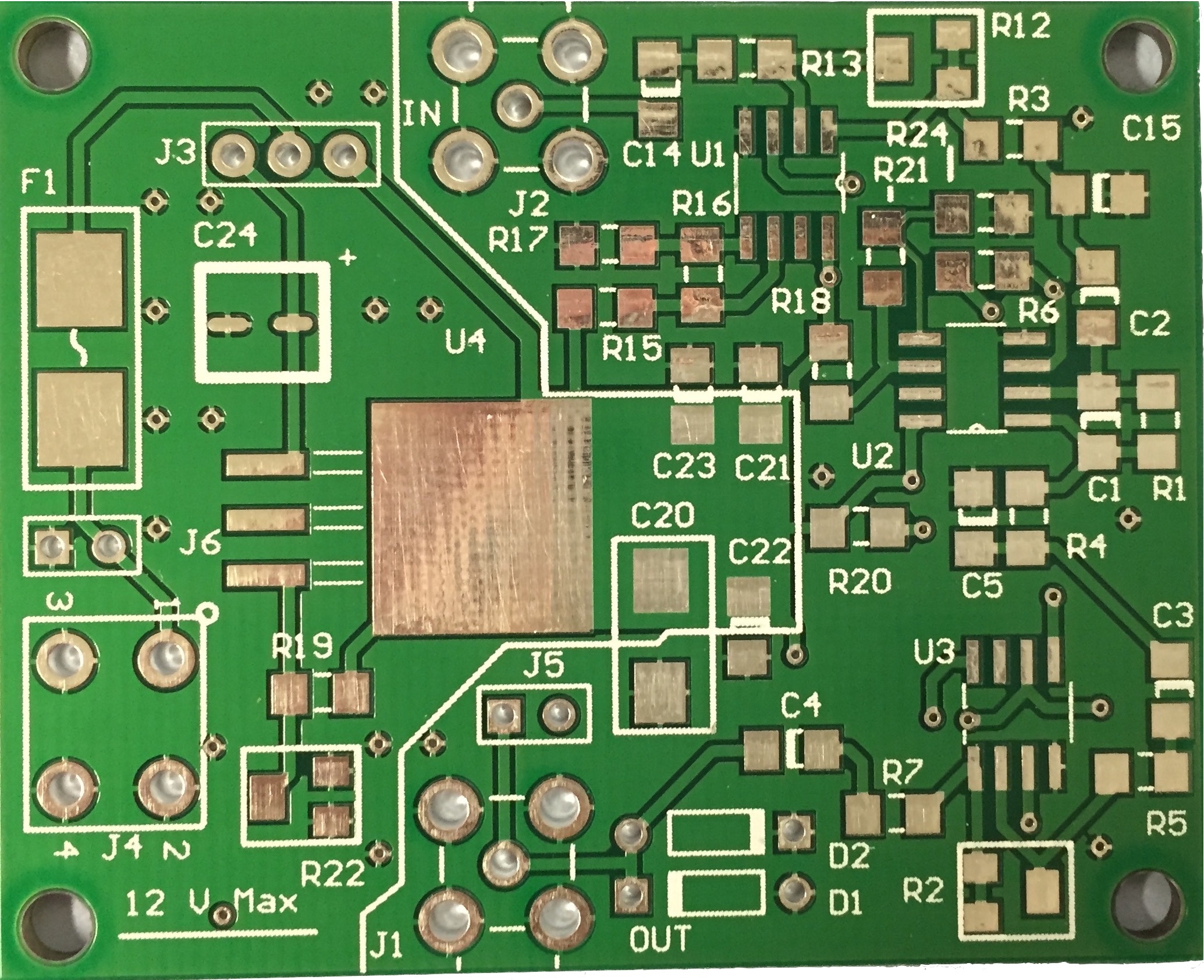

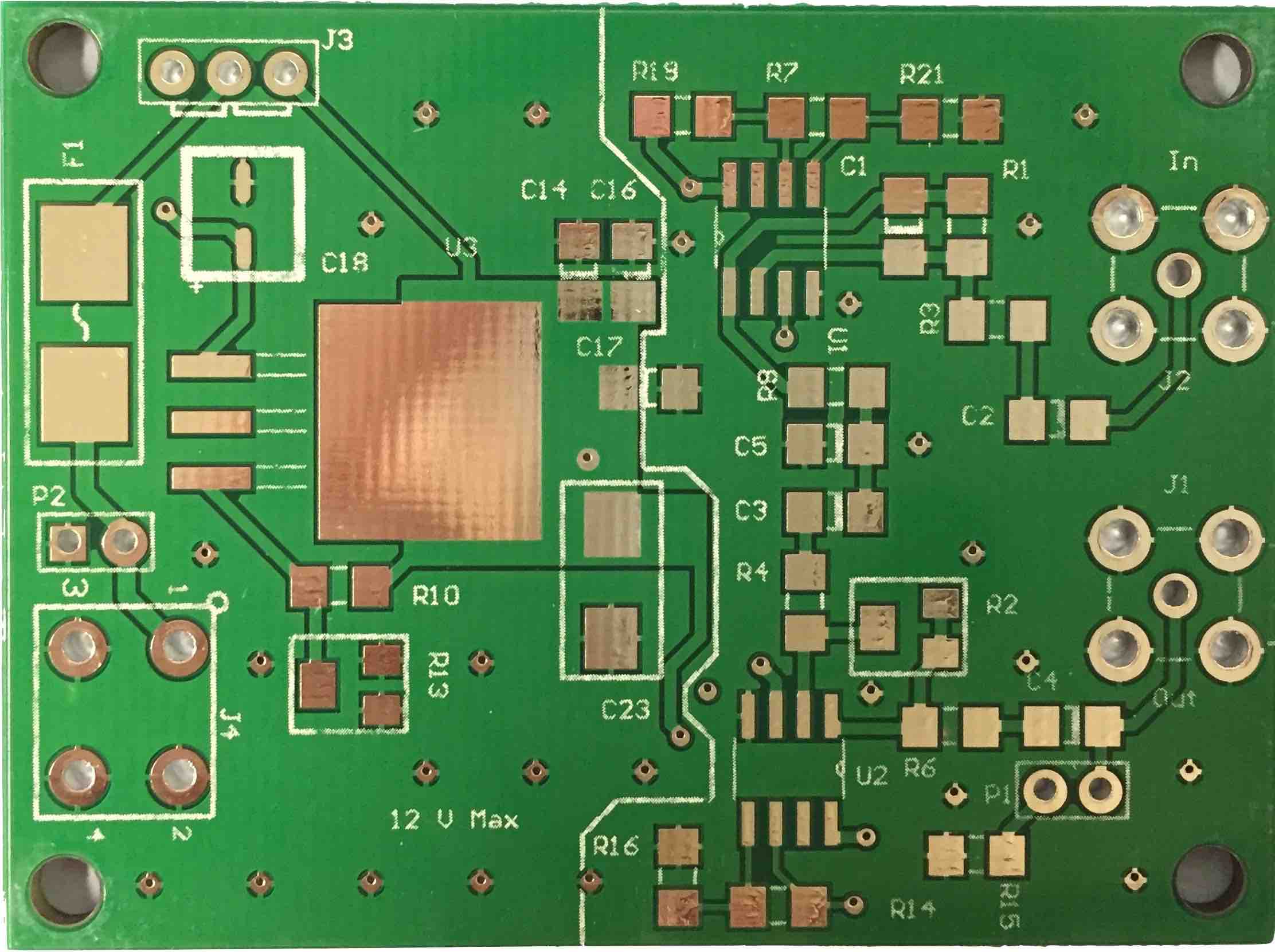

Powerline Transceiver Design: University of Waterloo

Jan 2015-Aug 2015, Advisor: Prof. Vincent Gaudet

• Assisted in In-Vehicular DC power-line communication (PLC) research

• Schematics and PCB designs of transmitter and receiver analog-front-end (AFE) boards

• Prototyped and characterized AFE transceivers in microelectronics laboratory

• Performed substantial circuit simulations and component selections for the AFE circuitry